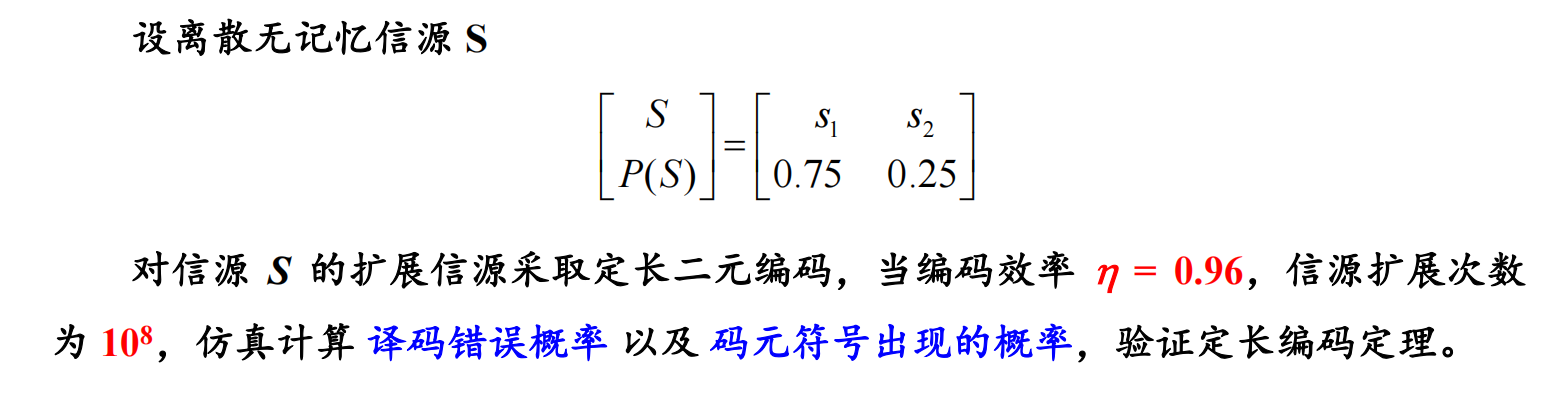

数电ModelSim作业3

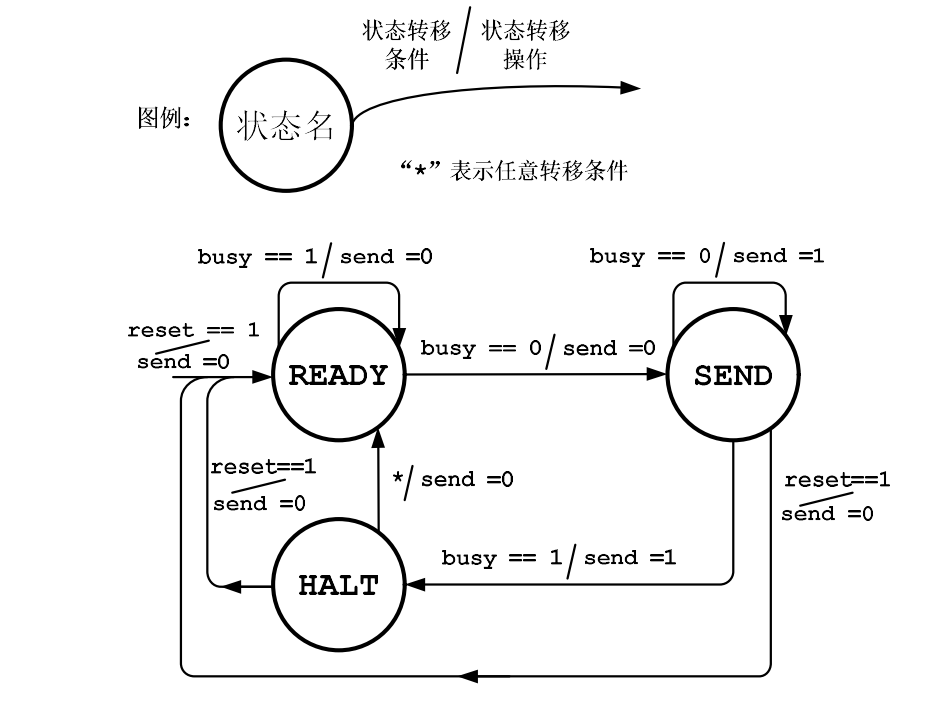

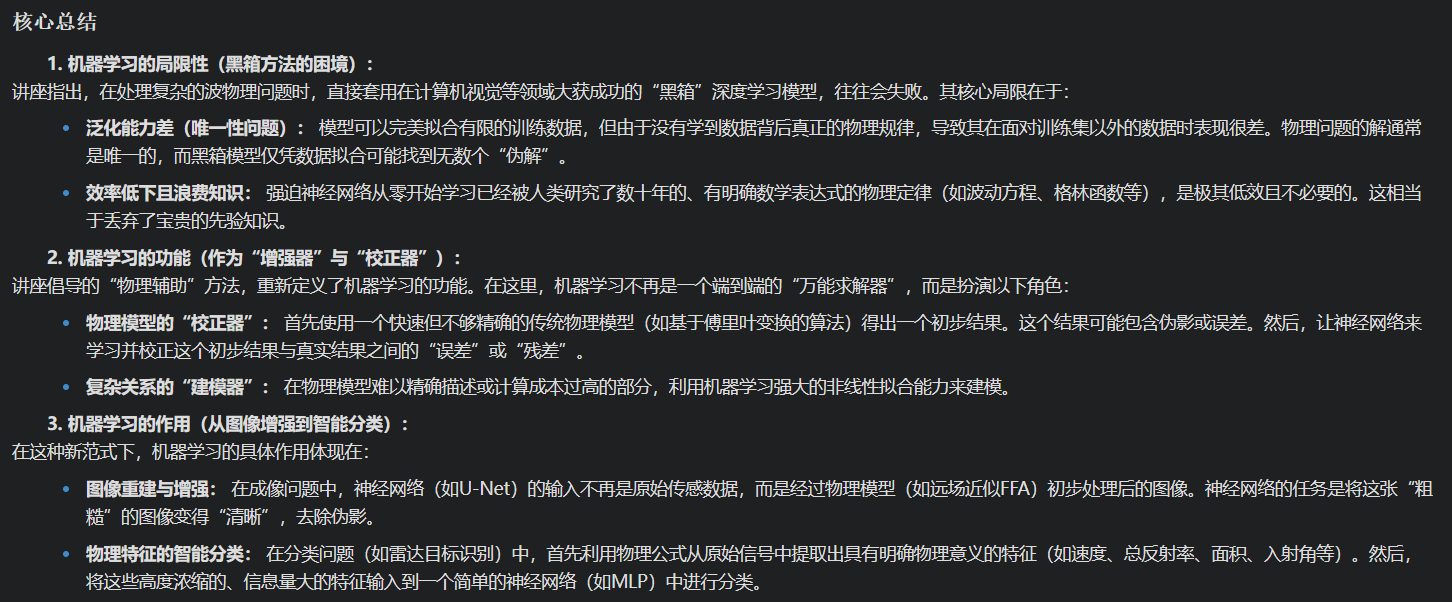

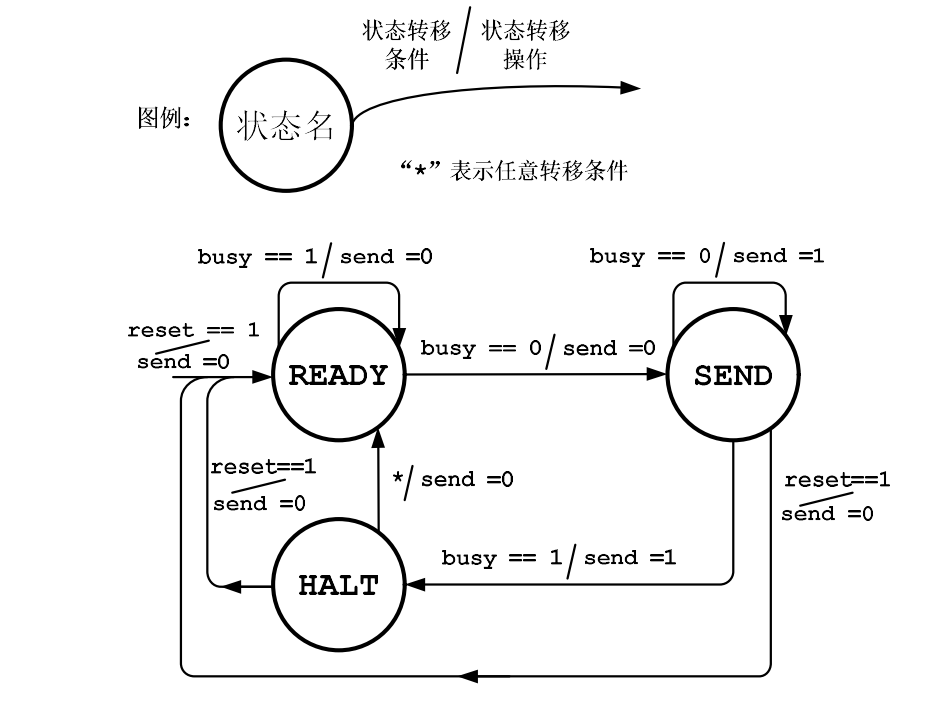

请实现如图所示的有限状态机,具体要求为:

请完成状态机的模块实现,并编写测试程序,分别测试 “READY->SEND->HALT->READY” 和 “READY->SEND->READY” 两条典型的状态转移路径。(请给出模块实现、测试代码和功能仿真结果)

一、新建Project

具体可以参考 “数电ModelSim作业1”

二、程序代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

| module tx_FSM (clock, reset, busy, send);

parameter [1:0] READY = 2'b00, SEND = 2'b11, HALT = 2'b10 ;

input clock ;

input reset, busy ;

output send ;

reg [1:0] state, next_state ;

always @( posedge clock or posedge reset ) begin

if(reset)

state <= READY;

else

state <= next_state;

end

reg send;

always @( busy or state )begin

send = 1'b0;

case(state)

READY:

if(busy)

next_state = READY;

else

next_state = SEND;

SEND:

if(reset)

next_state = READY;

else begin

if(busy)begin

next_state = HALT;

send = 1;

end

else begin

next_state = SEND;

send = 1;

end

end

HALT:

next_state = READY;

default:next_state = READY;

endcase

end

endmodule

|

三、测试代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

| `timescale 1ns/100ps

module tx_FSM_tb ;

parameter HALT = 2'b10 ;

parameter READY = 2'b00 ;

parameter SEND = 2'b11 ;

reg clock = 1 ;

wire send ;

reg busy ;

reg reset ;

initial begin

#40 reset = 1; busy = 0;

#50 reset = 0; busy = 1;

#50 reset = 0; busy = 1;

#200 reset = 0; busy = 0;

#50 reset = 1; busy = 0;

end

always #50 clock =~ clock;

tx_FSM #( HALT , READY , SEND )

DUT (

.clock (clock ) ,

.send (send ) ,

.busy (busy ) ,

.reset (reset ) );

endmodule

|

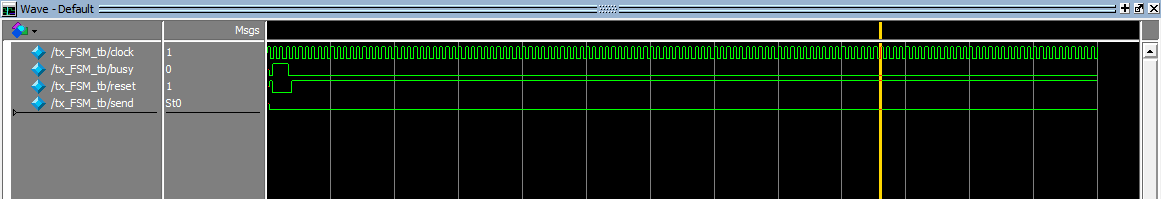

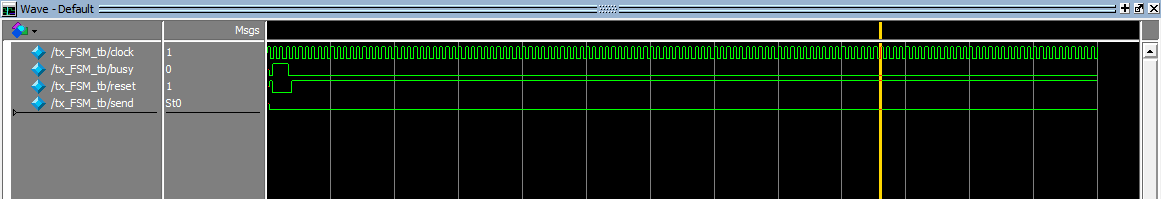

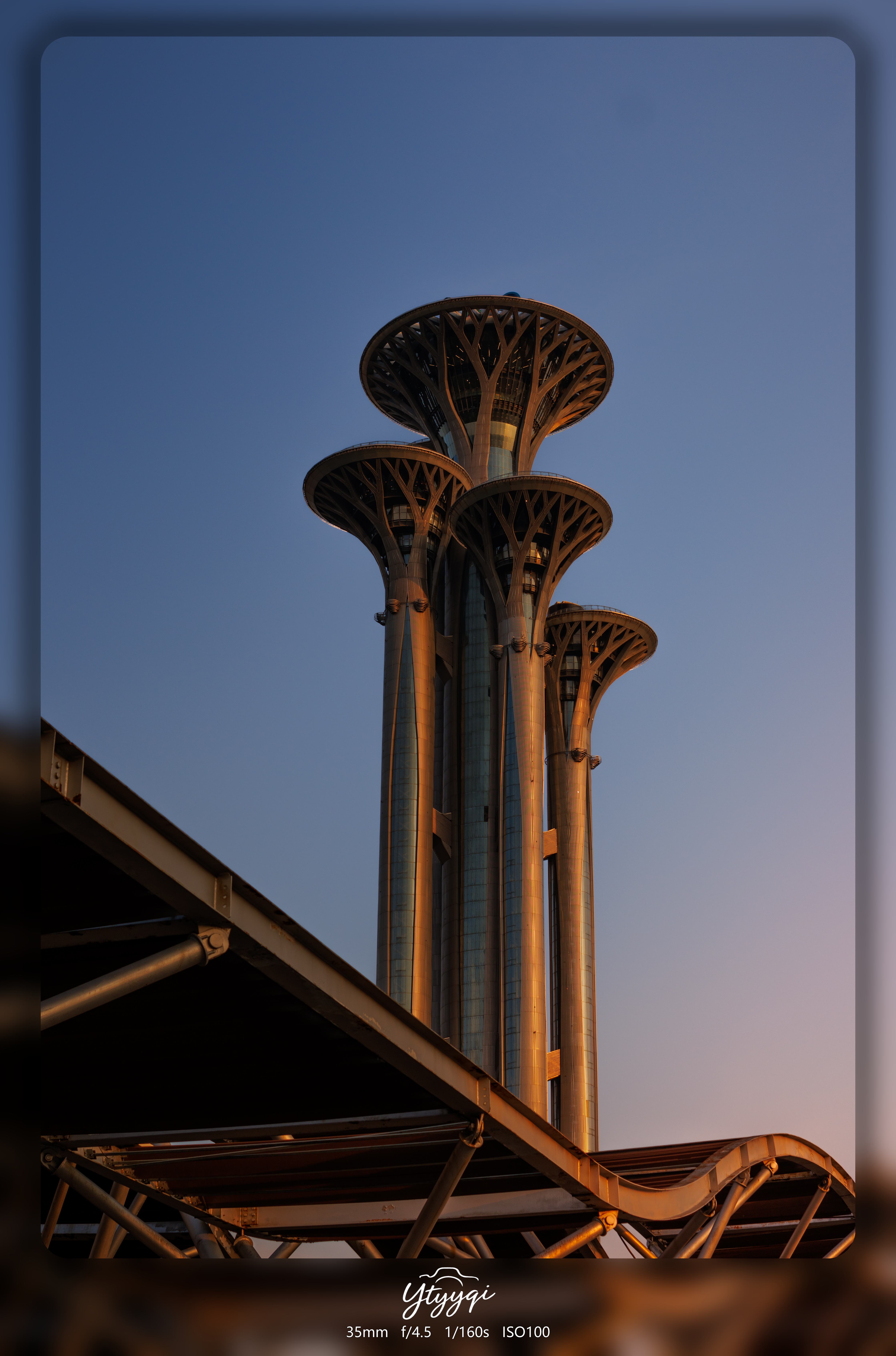

四、运行结果