数电ModelSim作业1

数电ModelSim作业1

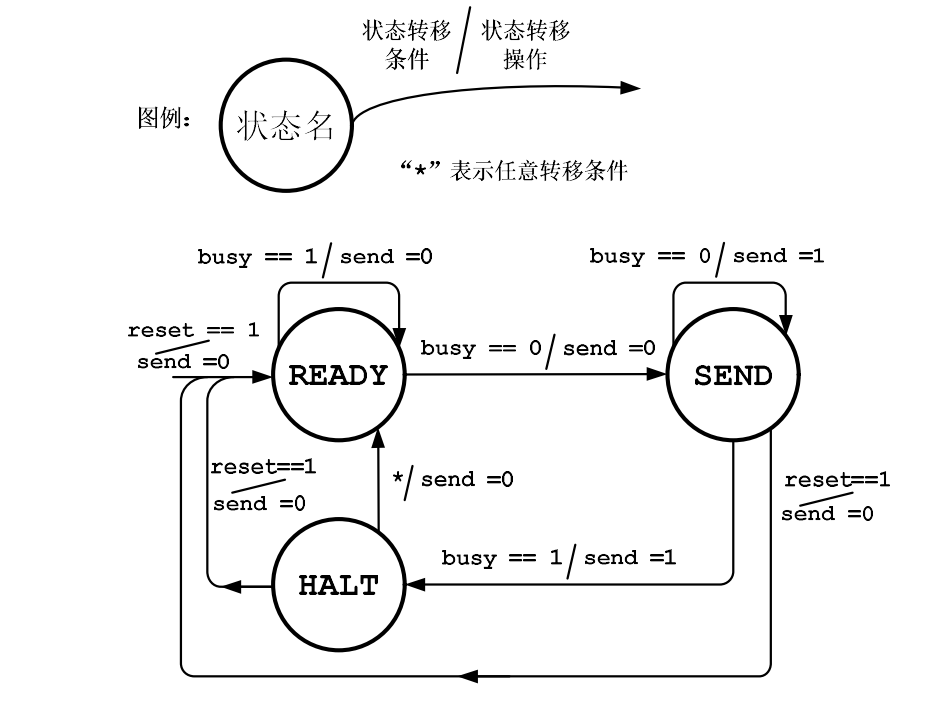

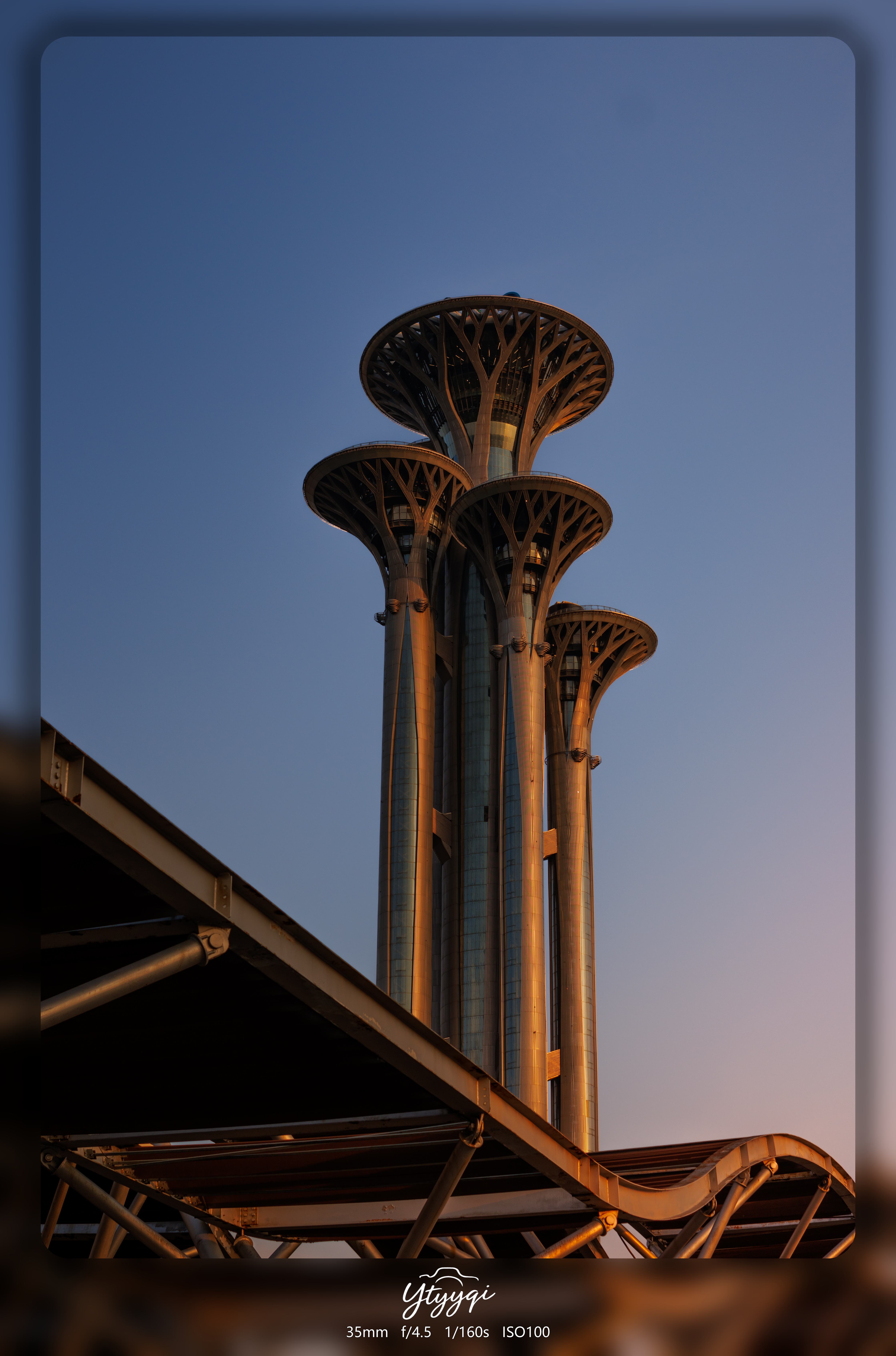

设某符号 Symbol 由 7 位信息码元和 1 位校验位组成,采用奇校验,即:发送端通过对校验位赋值,使符号中 “1” 的数目为奇数;如果符号在传输过程中受到干扰,有的码元可能发生翻转。

请用 Verilog HDL 语言设计一个奇校验检查电路,根据接收到符号中“1”的数目,判定该符号是否错误;请写出完整的模块。(设:该符号并行输入到接收端,电路的输入输出接口如图所示。)请用 Modelsim(或其它 EDA 编译/仿真器)实现模块、测试代码和功能仿真结果。

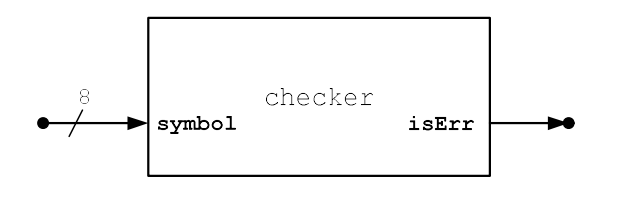

1、建立library

在建立工程(project)前,需要先建立工作库(library),一般命名为“work”,以后建立的所有project都在“work”下面工作。

1 | File -> new -> Library -> a new library -> 命名为“work” |

此时在Library中加入名为“work(empty)”的工作库。

2、建立project和新文件

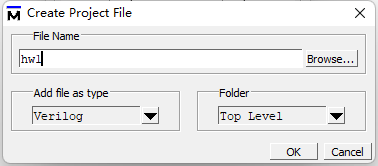

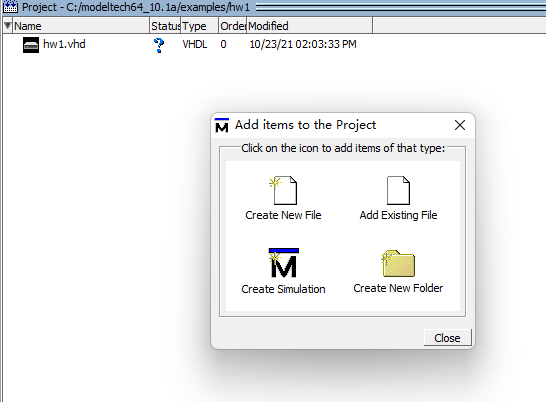

1 | File -> new -> Project -> 命名 -> Ok -> Create New File -> 命名 -> 把“Add file as type”改为“Verilog” -> OK -> Close |

在把新文件加入到Project以后,可以在项目中看到新建的文件,而下面的框框不会自己消失,需要单击“close”关闭。

3、编写代码并编译

双击刚建好的 .vhd 文件,可以进入编辑,输入程序后保存即可。

奇校验:

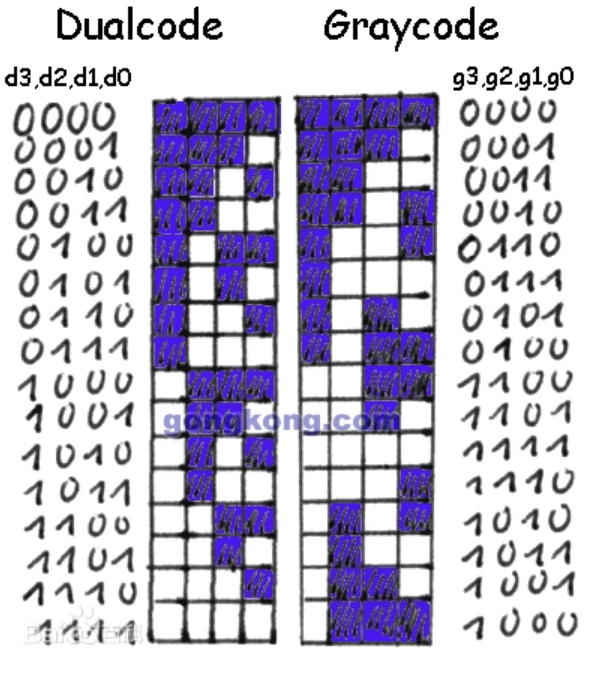

奇/偶校验(Parity Check)是数据传送时采用的一种校正数据错误的一种方式,根据被传输的一组二进制代码的数位中“1”的个数是奇数或偶数来进行校验。

如果输入的8位符号中有奇数个1,系统输出1;如果输入的8位符号中有偶数个1,系统输出0;

eg. 100010000 – 0;11000001 – 1;

实现办法:

可以把信号进行按位异或(如果a、b两个值不相同,则异或结果为1;如果a、b两个值相同,异或结果为0),把最后的结果赋值给b

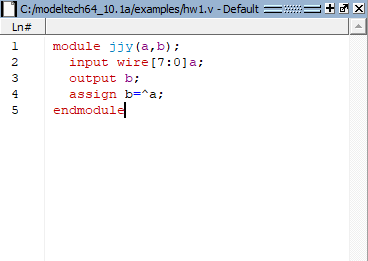

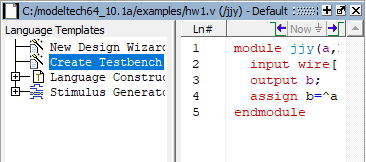

代码如下:

1 | module jjy(a,b); |

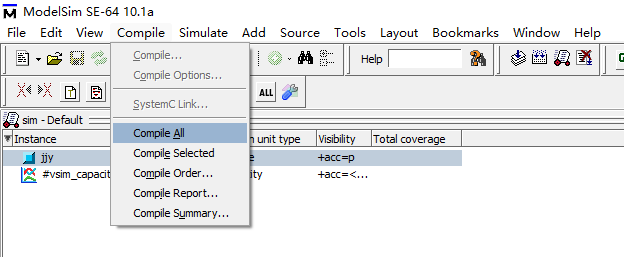

保存后,在菜单栏点击“Compile”中的“Compile All”。

4、编辑仿真测试代码

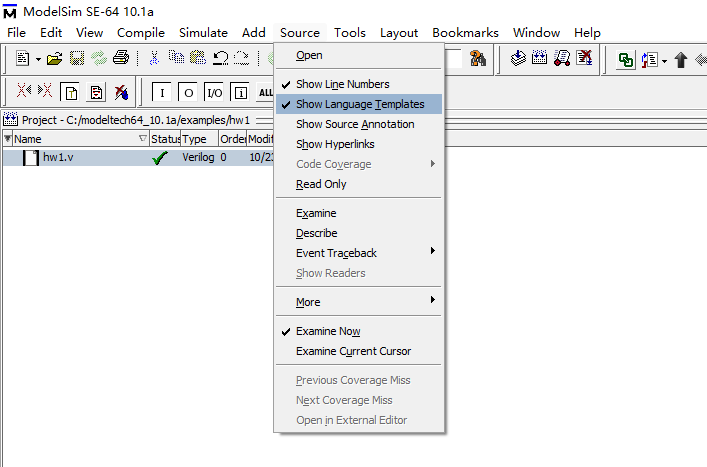

当光标处于编写程序的窗口时,菜单栏会出现“Source”,单击“Show Language Templates”

在弹出的窗口中选择“Create Testbench”。

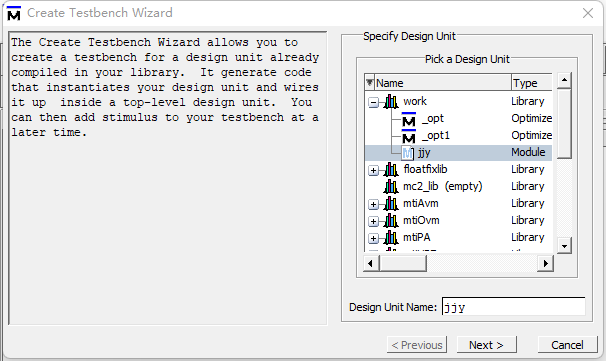

选择需要仿真测试的文件即可。

为测试所有8位信号,更改 xxx_tb.v内容如下后保存。

1 |

|

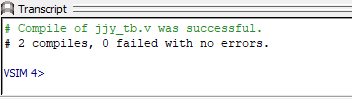

再在菜单栏点击“Compile”中的“Compile All”,会出现编译成功的结果

5、运行仿真测试

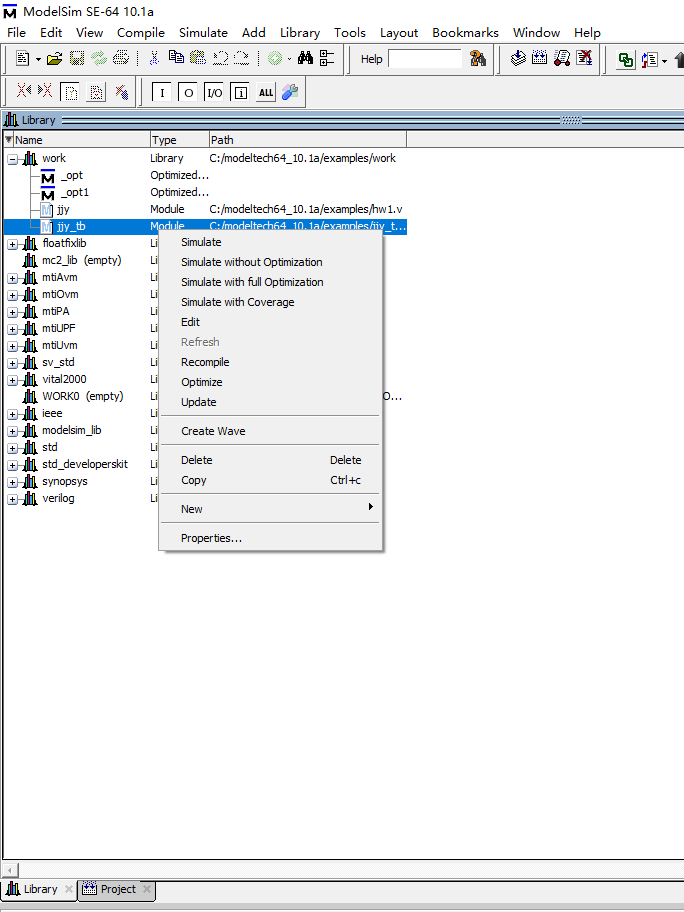

返回Library,右击xxx_tb,选择“Simulate”,多等一会。

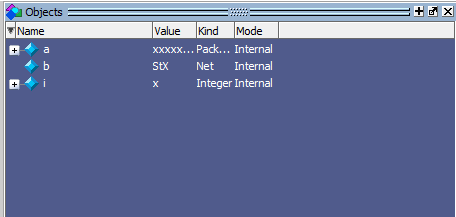

如果没有出现“Objects”窗口,在菜单栏中 View -> Objects 即可

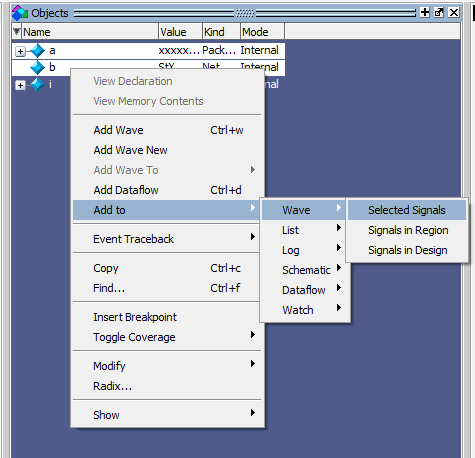

同时选中a、b,右击“Add to -> Wave -> Selected Signals”,

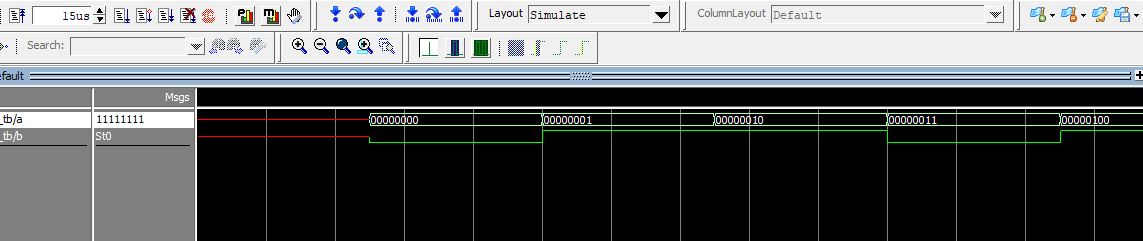

把时间改为 15us ,运行。